- 您现在的位置:买卖IC网 > Sheet目录3862 > PIC18F45J11-I/ML (Microchip Technology)IC PIC MCU FLASH 32K 2V 44-QFN

dsPIC30F3014/4013

DS70138G-page 112

2010 Microchip Technology Inc.

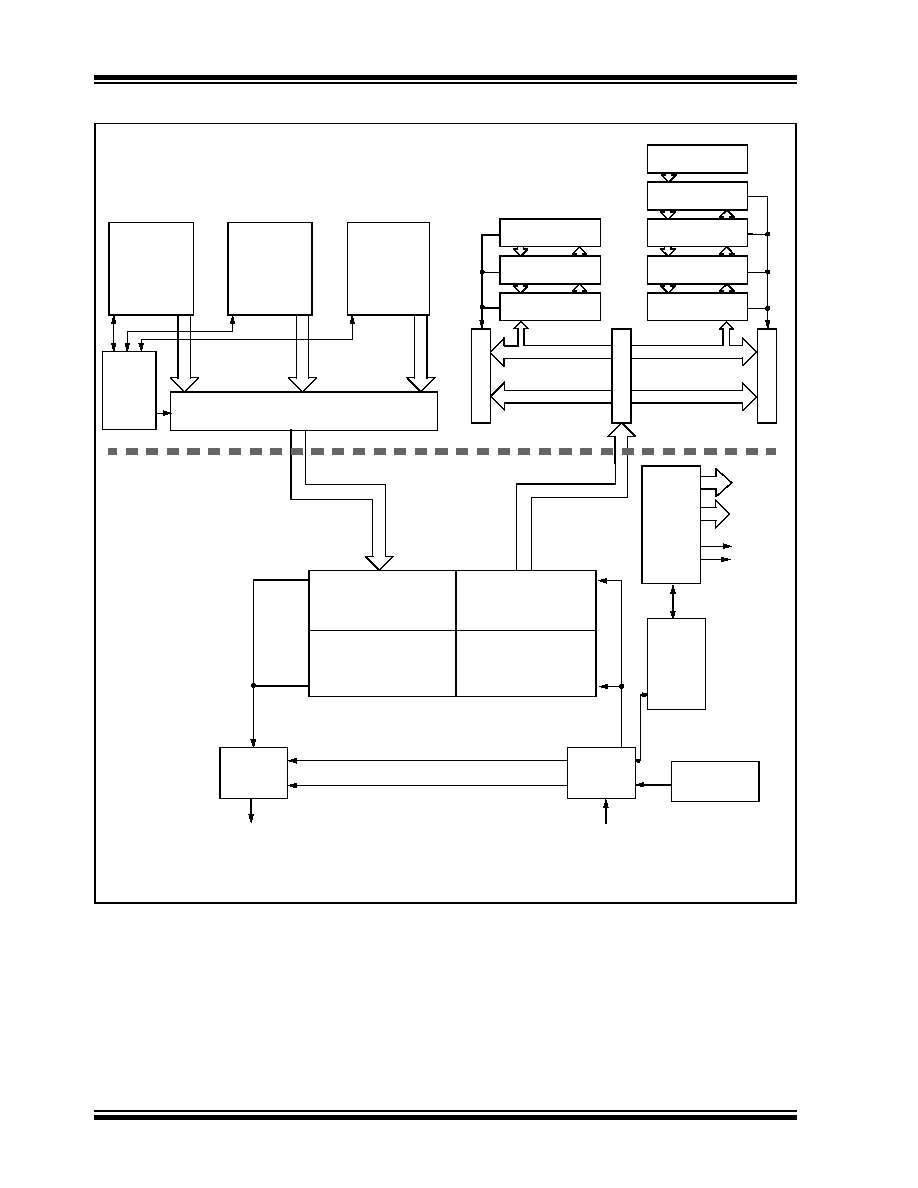

FIGURE 17-1:

CAN BUFFERS AND PROTOCOL ENGINE BLOCK DIAGRAM

Acceptance Filter

RXF2(2)

R(2)

X

B

1

A

c

e

p

t

A

c

e

p

t

Identifier

Data Field

Identifier

Acceptance Mask

RXM1(2)

Acceptance Filter

RXF3(2)

Acceptance Filter

RXF4(2)

Acceptance Filter

RXF5(2)

M

A

B

Acceptance Mask

RXM0(2)

Acceptance Filter

RXF0(2)

Acceptance Filter

RXF1(2)

R(2)

X

B

0

TX

R

E

Q

TXB2(2)

T

XABT

TX

LA

R

B

T

XERR

M

ESSAG

E

Message

Queue

Control

Transmit Byte Sequencer

TX

R

E

Q

TXB1(2)

T

XABT

TX

LA

R

B

T

XERR

M

ESSAG

E

TX

R

E

Q

TXB0(2)

T

XABT

TX

LA

R

B

T

XERR

M

ESSAG

E

Receive Shift

Transmit Shift

Receive

Error

Transmit

Error

Protocol

RERRCNT

TERRCNT

Err Pas

Bus Off

Finite

State

Machine

Counter

Transmit

Logic

Bit

Timing

Logic

CiTX(1)

CiRX(1)

Bit Timing

Generator

PROTOCOL

ENGINE

BUFFERS

CRC Check

CRC Generator

Note

1:

i = 1 or 2 refers to a particular CAN module (CAN1 or CAN2).

2:

These are conceptual groups of registers, not SFR names by themselves.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFW15R-2STE1

SFW15R-2STE1-FFC/FPC CONN

PIC18F26J11-I/ML

IC PIC MCU FLASH 64K 2V 28-QFN

PIC18F46K20-E/ML

IC PIC MCU FLASH 32KX16 44QFN

PIC24FJ64GA002-I/SO

IC PIC MCU FLASH 64KB 28SOIC

PIC16C711-04/P

IC MCU OTP 1KX14 A/D 18DIP

PIC18LF26K22-I/SP

IC PIC MCU 64KB FLASH 28SPDIP

PIC18F25K80-I/SP

MCU PIC 32KB FLASH 28SDIP

DSPIC33FJ12MC201-I/SS

IC DSPIC MCU/DSP 12K 20SSOP

相关代理商/技术参数

PIC18F45J11-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45J11T-I/ML

功能描述:8位微控制器 -MCU 32KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45J11T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45J50-I/ML

功能描述:8位微控制器 -MCU Full Spd USB 32KB 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45J50-I/PT

功能描述:8位微控制器 -MCU Full Spd USB 32KB 4KBRAM nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45J50T-I/ML

功能描述:8位微控制器 -MCU Full Spd USB 32KB 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45J50T-I/PT

功能描述:8位微控制器 -MCU Full Spd USB 32KB 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K20-E/ML

功能描述:8位微控制器 -MCU 32KB Flash 1536B RAM 25 I/O 8B RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT